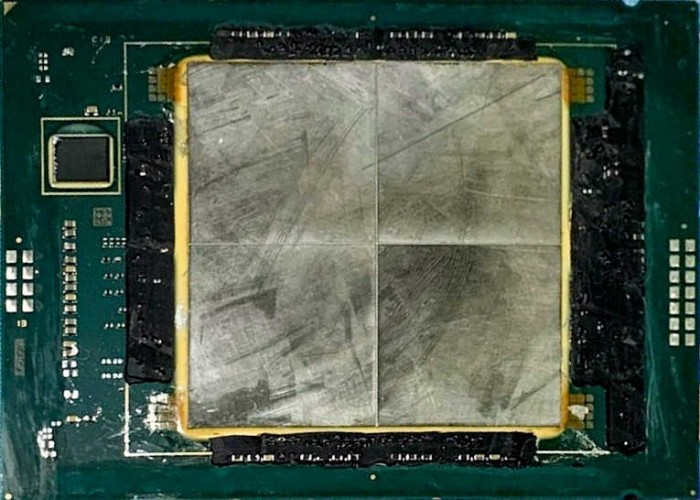

Intel’s next-generation scalable Xeon code-named Sapphire Rapids will be officially released next year. It will continue to use the 10nm process, but will fully upgrade the architecture, and the number of cores will also increase significantly. Earlier it was reported thatSapphire Rapids integrates up to 60 cores, divided into four groups, 15 in each group, Similar to AMD’s small chip design, but only 56 will be turned on,Later, it was said that up to 80 cores would be achieved.

Now, YuuKi_AnS, a netizen who has repeatedly exposed the specifications and physical objects of Sapphire Rapids, has announced its core photos for the first time, which is one of the four small chips.It can be clearly seen that there are indeed 15 cores, divided into three rows., But one of them will be blocked.

According to another report,This sample is also an early engineering sample in the ES0 stage, with a frequency of only 1.3GHz and an integrated 64GB HBM2E memory.

As for why the four cores were blocked at the factory, it is obviously out of the consideration of ensuring the yield and supply. The subsequent maturity does not rule out the possibility of full-blooded.

It seems that the 10nm SuperFin enhanced version process is still not very powerful.

According to the information currently available, Sapphire Rapids will be manufactured using a 10nm SuperFin enhanced version process. It will first support DDR5 memory, up to eight channels, 4800MHz frequency, and integrate HBM2 high-bandwidth memory for the first time, up to 64GB, and support the next generation of Optane persistent memory, random Access bandwidth is increased by up to 2.6 times.

In terms of technology, the first release supports PCIe 5.0, up to 80 channels, and the multi-channel interconnection channel is upgraded to four UPI 2.0, each with a bandwidth of 16GT/s. It also supports CXL 1.1 high-speed interconnection bus, and it can also be connected to independent via PCIe 5.0 and CXL. FPGA accelerator, the instruction set supports INT8, BFloat16 precision AMX, TMIUL.

The power consumption is also quite amazing, the TDP upper limit has been increased from 270W to 350W, and it is said that it can unlock 400W.

Visit the purchase page:

Intel Flagship Store

.